What is the Multiplexer?

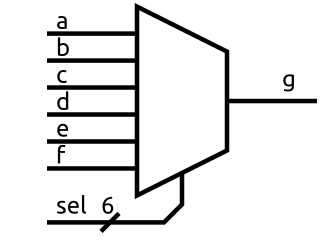

There are fundamental components, such as transistors and logic gates, and we can use them to create more useful things. Any digital circuit may be described using only logic gates. However, many recurring higher-level functions, such the adders, multipliers, and others used in binary math, have their own symbols. We'll examine the multiplexer, one of the essential components of FPGAs. Based on the value of its chosen input, a multiplexer chooses one input from a group. Here is its symbol:

To indicate that the sel line is six bits wide, a / is used. Although the multiplexer's input count can fluctuate, there is only ever one output. There will also be variations in the chosen input' encoding. Although the simpler circuit employs a one-hot encoding, you will typically view it as a binary number. A binary value with exactly one 1 present at all times is referred to as a one-hot encoding. What matters is where the 1 is placed. A decoder converts a binary value into a one-hot signal from the binary value. A one-hot value is converted into a binary number via an encoder. These can be used to enable binary values to be accepted by a one-hot multiplexer. FPGA including many family series such as Zynq-7000 SoC, FPGA Spartan-7, Artix-7 FPGA, Virtex-7 FPGAs, Kintex-7 FPGAs, and so on have different multiplexers to suit their design demand.

Encoding multiplexer by using some AND and OR gates

Consider how a one-hot encoded multiplexer could be created using just basic AND and OR gates. With the exception of the one with the b input, every AND gate will have an input that is 0 if the sel value is set to 000010, which means only sel[1] is 1. That indicates that regardless of the values of the inputs a, c, d, e, and f, each of those will always produce 0. The only relevant input is b. The output of the AND gate is 1 when b is 1, which is AND'd with a 1. The output of the AND gate is 0 when b is 0, which is AND'd with 1. In other words, the AND gate's output is just b.

.png)

In this schematic, the OR gate is seen with more than two inputs. This can be produced by building a tree of two input OR gates, where two inputs are combined using the OR operator, and the outputs are repeatedly combined using the OR operator to produce one output. If any of the inputs are 1, the output of a multi-input OR gate will behave as you would anticipate, being 1.

However, in this circuit, all inputs to the OR gate—aside from the input from the AND gate, whose output is b—are guaranteed to be zero. Thus, when b is 1 or 0, the OR gate will simply output a 1 and a 0 respectively. In other words, the output of the OR gate is simply b.

.png)

Verilog Multiplexer in a FPGA

A device called a multiplexer chooses one output from several inputs. A data selector is another name for it. The words "MUX" and "MPX" are used to describe a multiplexer. In communication systems, multiplexers are used to enhance the amount of data sent via a network in a given amount of time and bandwidth. It enables us to combine several data lines into a single data line.

It alternates between one of the numerous input lines before combining each one separately to produce the output. A control signal is used to determine which input line should be switched.

Multiplexer Structure

A multiplexer physically consists of n input pins, 1 output pin, and m control pins. n = 2^m. A multiplexer is also referred to as a data selector since its function is to choose one of the data input lines and deliver it to the output. Three methods can be used to build a multiplexer:

Logic gates make up digital multiplexers, transistors go into analog multiplexers, and rotating shafts go into mechanical switches or rotary switches.

.png)

The MUX itself functions as a digitally controlled multi-position switch where the data input is controlled by the binary code applied to the selected inputs and switched to the output.

VHDL Multiplexer in a FPGA

The multiplexer is implemented by using the VHDL when and else keywords. When the condition on the right of when (SEL = '1' - if SEL is equal to logic 1) is true, the signal on the left of when (A in our case) is assigned to the output signal (X in our example) using the when-else construct. assuming the condition is false, the output signal will instead be assigned to the signal to the right of the else (B) (assuming the signal on SEL is a logic 0).

A logic 1 on SEL will connect the 4-bit input bus A to the 4-bit output bus X as a result of this signal assignment. The 4-bit input bus B and the output bus X are connected by a logic 0 on the SEL pin.

Multiplexer Structure by using VHDL Multiplexer

The below image depicts the 2 to 1 multiplexer. The 4-bit input bus A will be connected to the 4-bit output bus X by a logic 1 on the SEL line. Input bus B and output bus X will be connected by a logic 0 on the SEL line.

.png)

Below is a diagram of a four-to-one multiplexer that multiplexes single (1-bit) signals. Which of the four inputs will be connected to the output is determined by the two SEL pins.

A(0) and X will be connected by SEL values of 00 and 01, respectively.

.png)

Multiplexer Applications

- Multiplexers in satellite communication use GSM communication to transport data from the satellite's computer system to the ground segment.

- It can also transform data from parallel to serial.

- The number of copper lines required to link the memory to other computer components is reduced by a computer.

- A multiplexer improves the efficiency of a communication system where there is a communication network by enabling the transmission of audio and video data over a single channel.

- A multiplexer performs the same function in optical fiber communication by employing a method called dense wavelength division multiplexing to integrate numerous fiber cables onto one fiber cable.